# VFC42 VFC52

# VOLTAGE-TO-FREQUENCY AND FREQUENCY-TO-VOLTAGE CONVERTER

# **FEATURES**

- V/F OR F/V CONVERSION

- TWO FREQUENCY RANGES

10kHz (VFC42)

100kHz (VFC52)

- LOW NONLINEARITY

±0.01% max (VFC42)

±0.05% max (VFC52)

- MINIMAL EXTERNAL COMPONENTS REQUIRED

Add only one external resister for V/F operation

- 6 DECADE DYNAMIC RANGE

- OUTPUT OTL/TTL/CMOS COMPATIBLE

# DESCRIPTION

VFC42 and VFC52 are hybrid microcircuits which can be connected as voltage-to-frequency or frequency-to-voltage converters. They provide a simple, low cost method of converting analog signals into an equivalent digital form. The digital output is an open collector which can be made compatible with DTL, TTL, or CMOS logic. The output is a train of constant-amplitude, constant-width pulses whose repetition rate is proportional to the amplitude of the analog input voltage. In the frequency-to-voltage mode the pulses become the input and the proportional DC voltage, the output.

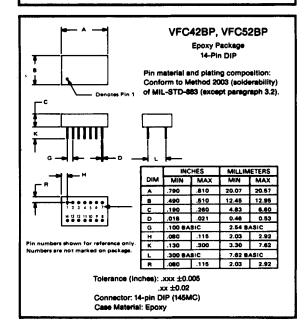

Both models are offered in epoxy (-25°C to +85°C) and hermetic metal (-25°C to +85°C and -55°C to +125°C) 14-pin DIP packages.

International Airport Industrial Park - P.S. Bux 11400 - Tuccon, Arizona 85734 - Tel. (802) 745-1111 - Tux: 910-952-1111 - Cable: BBRCORP - Talex: 66-6491

10

# THEORY OF OPERATION

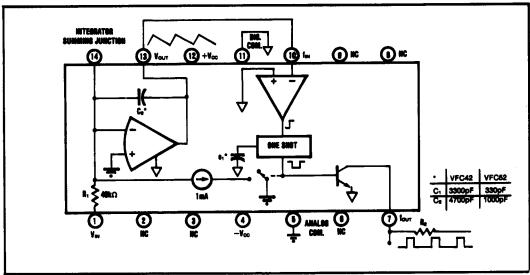

VFC42 and VFC52 hybrid voltage-to-frequency converters provide a digital pulse train output whose repetition rate is directly proportional to the analog input voltage. To understand the circuit's operation see Figure 1.

"The input amplifier is connected in an integrator configuration. When a positive input voltage is applied at  $V_{IN}$ , a constant current flows through the input resistor causing voltage at  $f_{IN}$  to ramp down toward zero, according to  $dV/dt = V_{IN}/R_1C_2$ . During this time the constant current sink is disabled by the switch. When the ramp reaches zero volts, the comparator causes the one-shot to fire. The  $f_{out}$  signal then changes states, going from logic 0 to logic 1 and the switch closes, enabling the constant current sink. Ramp voltage then changes direction and begins to ramp up. Since  $V_{IN}/R_1$  is always set to be less than ImA, current in the integrating capacitor flows toward the summing junction and ramp voltage

range of change will be

$$\frac{dV}{dt} = \frac{\left(\frac{V_{in}}{R_1}\right) - 1mA}{C_2}$$

Before the ramp voltage can saturate the input amplifier, the one-shot resets, disabling the current sink, changing the output state back to logic 0 and restarting the cycle.

To operate VFC42 and VFC52 as highly linear frequency-to-voltage converters, open the connection between Vour and  $F_{\rm IN}$  and connect  $V_{\rm IN}$  to  $V_{\rm OUT}$ . The input frequency should be coupled through a capacitor to  $f_{\rm IN}$ . A positive output voltage proportional to  $f_{\rm IN}$  will be generated at the  $V_{\rm OUT}$  connection. An external capacitor connected between pins 13 and 14 (paralleling C2) should be added to reduce output ripple. Refer to Operating Instructions for detailed information on F/V operation.

FIGURE 1. Functional Block Diagram.

# **DISCUSSION OF SPECIFICATIONS**

# LINEARITY

Linearity, the maximum deviation of the actual transfer function from a straight line drawn between the end points (full scale input and zero input), is the true measure of a FVC's performance and is a function of full scale frequency. The high linearity of VFC42 and VFC52 makes these devices an excellent choice for use in A/D converters with 10 (0.05%) and 12 bit (0.012%) accuracy and for highly accurate analog data transfer over long lines in noisy environments.

## FREQUENCY STABILITY VS TEMPERATURE

Frequency stability vs temperature is expressed as parts per million of full scale range per °C. Since frequency drift is a function of the specified temperature range, the "SM" models will meet the lower drift specifications of the "BM" models over the narrower -25°C to +85°C temperature range. Error sources do not drift linearly over temperature, consequently the units drift much less at higher temperatures.

#### **RESPONSE TIME**

Response time of VFC42 and VFC52 to input signal level changes is specified for a full scale step and is 1µsec plus 1 period of the new frequency. Typical settling time to within rated linearity for a positive input voltage step of +10V is 101µsec for VFC42 and 11µsec for VFC52.

# **SPECIFICATIONS**

## **ELECTRICAL**

Specifications at  $T_A = \pm 25^{\circ}$  C, and  $\pm 15$ VDC power supplies unless otherwise noted.

| MODEL                                                                                   | VFC42                                                                  |                                       |              |                | VFC52          |              |                         |  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------|--------------|----------------|----------------|--------------|-------------------------|--|

|                                                                                         | MIN                                                                    | TYP                                   | MAX          | MIN            | TYP            | MAX          | UNITS                   |  |

| Full Scale Frequency                                                                    |                                                                        | 10                                    |              |                | 100            |              | kHz                     |  |

| INPUT                                                                                   |                                                                        |                                       |              |                |                |              |                         |  |

| Analog Input (V/F)                                                                      |                                                                        |                                       |              |                |                |              |                         |  |

| Voltage Range                                                                           | 0                                                                      |                                       | 10           | 0              |                | +10          | V.                      |  |

| Current Range                                                                           | 0                                                                      | 6                                     | +0.25<br>8   | 0              | 6              | +0.25<br>8   | mA<br>nA                |  |

| Input Bias Current (pin 14) Inverting Input<br>Input Offset Voltage (trimmable to zero) |                                                                        | 100                                   | 200          | 1              | 100            | 200          | ] <u>"</u>              |  |

| Input Impedance (pin 1)                                                                 | 32                                                                     | 40                                    | 48           | 32             | 40             | 48           | kΩ                      |  |

| Frequency Input (F/V) (pin 10)                                                          |                                                                        |                                       |              |                |                |              |                         |  |

| Logic Lévels: Logic "0"                                                                 | -Vcc                                                                   |                                       | 0.6          | -V∞            |                | -0.6         | V                       |  |

| Logic "1"                                                                               | +1.0                                                                   | İ                                     | +Vcc         | +1.0           |                | +Voc         | V                       |  |

| Pulse Width Range (t <sub>2</sub> , Fig. 6)<br>Impedance                                | 0.1<br>1    10                                                         | 1.2    10                             | 15           | 0.1<br>1    10 | 1.2    10      | 1.5          | μsec<br>MΩ    pF        |  |

| TRANSFER CHARACTERISTICS                                                                | <u> </u>                                                               | · · · · · · · · · · · · · · · · · · · | <u> </u>     |                |                |              |                         |  |

| Transfer Functions                                                                      | $t_{OUT} = V_{IN} (1.00 \times 10^3)$                                  |                                       |              | fou            | Hz             |              |                         |  |

|                                                                                         | $V_{OUT} = f_{IN} (10 \times 10^{-4})$                                 |                                       |              | Vo             | VDC            |              |                         |  |

| Accuracy                                                                                |                                                                        | ٠. ا                                  |              |                |                |              |                         |  |

| Full Scale Gain (adjustable to zero)  Linearity Error: 0.01Hz ≤ F ≤ 10kHz               | 1                                                                      | 0.1<br>0.005                          | 0.2<br>0.01  |                | 0.1            | 0.2          | % of FSR <sup>(1)</sup> |  |

| U.01Hz ≤ F ≤ 10kHz                                                                      | I                                                                      | 0.005                                 | J            |                | 0.025          | 0.05         | % of FSR                |  |

| Offset Error (pin 1)                                                                    |                                                                        | 0.001                                 | 0.002        |                | 0.001          | 0.002        | % of FSR                |  |

| Power Supply Sensitivity <sup>(2)</sup>                                                 |                                                                        |                                       | 0.015        |                |                | 0.015        | % of FSR/%              |  |

| Temperature Stability                                                                   |                                                                        |                                       |              |                |                | 1            |                         |  |

| Analog Input                                                                            | ŀ                                                                      |                                       |              |                |                |              |                         |  |

| Full Scale Drift (gain and offset)                                                      | l                                                                      | 145/150                               | ±30/±100     | 1              | ±20/±50        | ±30/±150     | ppm/°C                  |  |

| Grade: BP (hot/cold) <sup>(3)</sup><br>BM                                               |                                                                        | ±15/±50<br>±15/±50                    | ±30/±100     | İ              | ±20/±50        | ±30/±150     | ppm/*C                  |  |

| SM                                                                                      |                                                                        | ±30/±60                               | ±50/±100     | i              | ±30/±60        | ±50/±150     | ppm/°C                  |  |

| Offset Drift                                                                            |                                                                        |                                       |              |                |                |              | , pp                    |  |

| Grade: BP                                                                               | l                                                                      | ±1                                    | ±3           |                | ±1             | ±3           | ppm of FSR/*            |  |

| вм                                                                                      |                                                                        | ±1                                    | ±3           |                | ±1             | ±3           | ppm of FSR/*            |  |

| SM                                                                                      |                                                                        | ±1                                    | ±3           |                | ±1             | ±3           | ppm of FSR/*            |  |

| Frequency input                                                                         | 1                                                                      |                                       |              | ŀ              |                | 1            | ļ                       |  |

| Full Scale Drift (gain and offset) Grade: BP (hot/cold) <sup>(3)</sup>                  |                                                                        | ±15/±50                               | ±30/±100     | ļ              | ±20/±50        | ±30/±150     | ppm/°C                  |  |

| BM                                                                                      | ļ                                                                      | ±15/±50                               | ±30/±100     |                | ±20/±50        | ±30/±150     | ppm/°C                  |  |

| SM                                                                                      |                                                                        | ±30/±60                               | ±50/±100     |                | ±30/±60        | ±50/±150     | ppm/°C                  |  |

| Dynamic Response                                                                        |                                                                        |                                       |              |                |                |              |                         |  |

| Settling Time to within linearity                                                       |                                                                        | l                                     |              |                | [<br>          | 1            |                         |  |

| specification for full scale input step Overload Recovery Time                          | 1 period of new frequency + 1µsec<br>1 period of new frequency + 1µsec |                                       |              | 1 period o     | i              |              |                         |  |

| OUTPUT                                                                                  | 1 period                                                               | Or new mequent                        | γ τ ιμοσυ    | period         | of new frequen | Cy T IprodC  |                         |  |

| Voltage Output                                                                          |                                                                        |                                       |              |                |                | l            |                         |  |

| Voltage Range (I₀ ≤ 5mA)                                                                | 0 to +10                                                               |                                       |              | 0 to +10       |                | 1            | l v                     |  |

| Output Current (Vo ≤ 7V)                                                                | +10                                                                    |                                       |              | +10            |                | 1            | mA.                     |  |

| Output Impedance (closed loop)                                                          |                                                                        |                                       | 1            |                |                | 1            | Ω                       |  |

| Capacitive Load                                                                         |                                                                        |                                       | 100          |                |                | 100          | pF                      |  |

| Frequency Output (open collector)                                                       |                                                                        |                                       |              |                |                | 1            | l                       |  |

| Pulse Characteristics: Logic "1"                                                        | ا م ا                                                                  |                                       | +VPULL-UP    | 0              |                | +Vpull-up    | l v                     |  |

| Logic "0" (at l <sub>o</sub> ≤ −8mA)<br>Pulse Width                                     | 0<br>20                                                                | 25                                    | +0.4         | 2.0            | 2.5            | +0.4         | ν<br>μsec               |  |

| Output Sink Current (Logic "0", ≤ 0.4V)                                                 | ا ت                                                                    | 25                                    | 8            | 2.0            | 2.5            | 8            | mA                      |  |

| Output Leakage Current (Logic "1")                                                      |                                                                        |                                       | 1            |                |                | Ĭ            | μA                      |  |

| Fall Time (I <sub>OUT</sub> = -5mA, C <sub>LOAD</sub> = 500pF)                          |                                                                        |                                       | 400          |                |                | 400          | nsec                    |  |

| POWER SUPPLY REQUIREMENTS                                                               |                                                                        |                                       |              |                |                |              |                         |  |

| Rated Supplies                                                                          | , _                                                                    | ±15                                   |              | , _            | . ±15          |              | v                       |  |

| Supply Range Supply Drain (independent of operating frequency)                          | ±9                                                                     | ±6.5                                  | ±20<br>±7.5  | ±9             | ±6.5           | ±20<br>±7.5  | V<br>mA                 |  |

|                                                                                         |                                                                        | ±0.5                                  | ±1.5         |                | ±6.5           | ±1.5         | I MA                    |  |

| TEMPERATURE RANGE                                                                       | 05                                                                     |                                       |              |                |                |              |                         |  |

| Specification: BP, BM<br>SM                                                             | 25<br>56                                                               |                                       | +85<br>±136  | -25<br>-55     |                | +85          | *c                      |  |

| SM<br>Operating: BM, SM                                                                 | 55<br>55                                                               |                                       | +125<br>+125 | −55<br>−55     |                | +125<br>+125 | l °c                    |  |

| BP                                                                                      | -55                                                                    |                                       | +100         | -55<br>-55     |                | +100         | l •č                    |  |

| Storage: BM, SM                                                                         | -55                                                                    |                                       | +125         | -55            |                | +125         | l ∙č                    |  |

| BP                                                                                      | -25                                                                    |                                       | +85          | -25            |                | +85          | l •č                    |  |

NOTES: (1) % of FSR = % of Full Scale Range. (2) Rated at full scale input and ±15V supplies. (3) Hot = +20° C to highest rated temperature; cold = lowest rated temperature to +20° C.

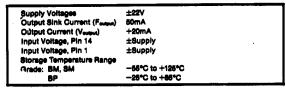

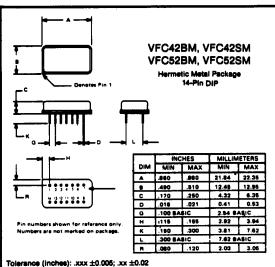

#### **MECHANICAL**

Connector: 14-pin DIP (145MC)

Case Material: Base - gold plated kover, Cap - nickel-plated kover or stee Pin meterial and pleting compositions: Conforms to MIL-STD-883, Method 2003 (solderability) except paragraph 3.2 (aging).

Hermeticity: Conforms to MIL-STD-883, Method 1014, Condition C, Step 1, Fluorocarbon (gross leak).

# **OPERATING INSTRUCTIONS**

VFC42 and VFC52 can be connected for either V/F or F/V operation. Only one external component, the output pull-up resistor, is required for V/F operation. F/V operation requires the pull-up resistor and input biasing components. Gain error is the most significant error in either configuration and may be nulled out with the optional trim circuit (R<sub>x</sub> and R<sub>y</sub>). The offset error is laser trimmed at the factory and no external adjustment is required.

<u>Power Supply Consideration</u>: Power supplies stable to within  $\pm 1\%$  are recommended to maintain conversion accuracy. Each supply should be bypassed with  $0.01\mu F$  capacitors located as close to the VFC as possible.

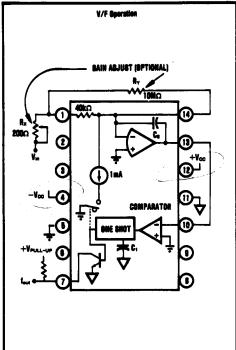

#### **VOLTAGE-TO-FREQUENCY OPERATION**

Calculating the Value of Pull-Up Resistor, R. The open collector output can be used to drive DTL, TTL, CMOS or discrete circuits. The maximum collector current allowed for TTL circuits in logic 0 is 8mA. R. may be calculated by this equation:

$$R_P \min = V \text{ pull-up/(8mA} - i_{LOAD}).$$

A 10% carbon composition resistor is suitable for this purpose. The collector current may be as great as 30mA if a logic 0 voltage of 1.0V is tolerable.

Gain Adjustment Procedure: Connect R<sub>X</sub> and R<sub>Y</sub> as shown in Connection Diagram. Apply positive full scale voltage to the input and adjust R<sub>X</sub> until 10kHz ±1Hz (VFC42) or 100kHz ±10Hz (VFC52) is obtained at f<sub>OUT</sub>. R<sub>X</sub> and R<sub>Y</sub> should have temperature coefficients of <500ppm. These external components will add less than 5ppm/°C to temperature drift.

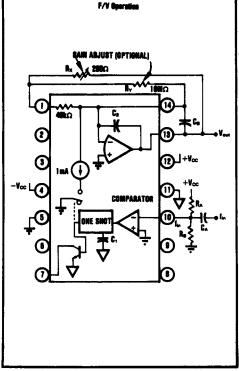

## FREQUENCY-TO-VOLTAGE OPERATION

Input Characteristics: VFC42 and VFC52 can be connected as frequency-to-voltage converters as shown in Connection Diagram.  $f_{IN}$  should be a positive pulse train with minimum pulse width of  $1.0\mu\text{sec}$  and rise and fall times of  $\leq 300\text{nsec}$ . The input train  $(f_{IN})$  is differential and applied to the input of the comparator (pin 10) (see Figure 2). Threshold voltage of the comparator lies between -0.6 and +1.0V. When comparator input is less than -0.6V it triggers the one-shot.

Selecting  $R_A$ ,  $R_B$ , and  $C_A$  input components  $R_A$ ,  $R_B$  and  $C_A$  are selected so that the trigger voltage  $(V_T)$  is more negative than -0.6V and transition time  $(t_2)$  is between

TABLE I. F/V Input Component Selection

| input<br>Type | Veerut (V) |                | Ī.,          | VFC42                  |            |                        | VFC52                  |                       |                        |

|---------------|------------|----------------|--------------|------------------------|------------|------------------------|------------------------|-----------------------|------------------------|

|               | Low        | High           | V24A2<br>(V) | R <sub>A</sub><br>(kΩ) | Re<br>(kΩ) | C <sub>A</sub><br>(pF) | R <sub>A</sub><br>(kΩ) | R <sub>a</sub><br>(Ω) | C <sub>A</sub><br>(pF) |

| TTL           | ≤+0.4      | ≥+2.8          | +1.1         | 12                     | 1.0        | 1000                   | 8.2                    | 680                   | 680                    |

| 5V<br>CMOS    | ≲+0.5      | ≥+4.5          | +1.2         | 18                     | 1.6        | 2200                   | 9.1                    | 820                   | 680                    |

| 10V<br>CMOS   | ≤+1.0      | ≥+ <b>9</b> .0 | +1.1         | 12                     | 1.0        | 2200                   | 6.2                    | 510                   | 680                    |

| 15V<br>CMOS   | ≤+1.5      | ≥+13.5         | +1.1         | 12                     | 1.0        | 2200                   | 6.2                    | 510                   | 680                    |

$0.3\mu sec$  and  $15\mu sec$  for VFC42 and between  $0.3\mu sec$  and  $1.5\mu sec$  for VFC52. Table I give values for input components for several common signal sources. Values for  $R_A$ ,  $R_B$  and  $C_A$  may be selected by the user when input signal characteristics differ from those listed. Conditions described above for trigger voltage and transition time must be observed.

Equations to calculate trigger voltage and transition time are:

$$\begin{split} V_T &= V_B + V_{in} \, (e^{-t} i/\tau - 1) \\ t_2 &= -\tau ln \, [ \, \frac{1 - V_B}{V_{in} \, (e^{-t} i/\tau - 1)} \, ] \end{split}$$

V<sub>B</sub> = Bias voltage on pin 10

V<sub>in</sub> = Input pulse amplitude

$t_1 = Input pulse width$

$\tau$  = Time constant of R<sub>A</sub>, R<sub>B</sub> C<sub>A</sub> as connected

If input pulse amplitude is greater than  $+V_{\rm CC}-1V$ , a voltage larger than  $+V_{\rm CC}$  will be applied to pin 10. Since this may damage the unit, a diode connected across  $R_{\rm A}$  with the cathode tied to  $+V_{\rm CC}$  is required.

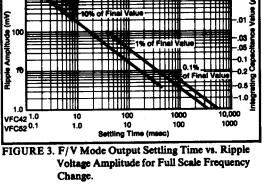

Output Characteristics: Selecting  $C_B$ : Output ripple voltage amplitude is it-versely proportional to the input frequency and to the value of the integrating capacitance,  $C_2 + C_B$ . Conversely, time required for the output to settle is directly proportional to the value of  $C_2 + C_B$  and is least with small values of  $C_2 + C_B$ . There is, therefore, a trade-off between output ripple amplitude and output settling time.

Because ripple amplitude is greatest at lowest input frequency it is at this point where the trade-off will usually be made. Ripple voltage and integrating capacitance value are related in this manner:

$$C_B = \frac{-(25 \times 10^{-6})t_{esc}}{\ln\left[1 - \frac{V_{Ripple}}{30V}\right]} farads$$

where t is equal to  $25\mu$ sec in the VFC42 and  $2.5\mu$ sec in the VFC52 and C is the integrating capacitance.

Calculating output response time versus integrating capacitance is an iterative process and is plotted in Figure 3. These curves are for zero to full scale input frequency transitions. If faster response time with lower ripple voltage is desired, a low-pass filter can be connected in series with the output.

Gain Adjustment Procedure: Connect  $R_X$  and  $R_Y$  as shown in Connection Diagram. Apply full scale frequency to the input and adjust  $R_X$  until the full scale voltage is  $\pm 10V \pm 1mV$  (discounting ripple).  $R_X$  and  $R_Y$  should have temperature coefficients of < 500ppm. These external components will add less than 5ppm/°C to temperature drift.

# +1.0V 0.60

FIGURE 2. F/V Input Waveforms.

# **APPLICATION**

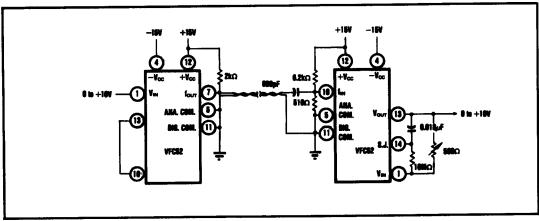

VFC42 and VFC52 can be used to convert analog data into a digital pulse train for transmission over long lines through high EMI environments. Illustrated in Figure 4 is a V/F, F/V combination that can be used to transmit analog data of 0 to  $\pm 10V$  over a  $100\Omega$  shielded, twistedpair. The voltage ripple amplitude at the output will be 10mV for a 10V output and the settling time for a full scale 0 to +10V change is 60 milliseconds.

FIGURE 4. V/F, F/V Data Transmission Circuit.

10