Discussion

T-49-19-07

Super8™ MCU ROMIess, ROM, and Prototyping Device with EPROM Interface

Z8800, Z8801, Z8820, Z8822

# **FEATURES**

- Improved Z8<sup>®</sup> instruction set includes multiply and divide instructions, Boolean and BCD operations.

- Additional instructions support threaded-code languages, such as "Forth."

- 325 byte registers, including 272 general-purpose registers, and 53 mode and control registers.

- Addressing of up to 128K bytes of memory.

- Two register pointers allow use of short and fast instructions to access register groups within 600 nsec.

- Direct Memory Access controller (DMA).

- Two 16-bit counter/timers.

- Up to 32 bit-programmable and 8 byte-programmable I/O lines, with 2 handshake channels.

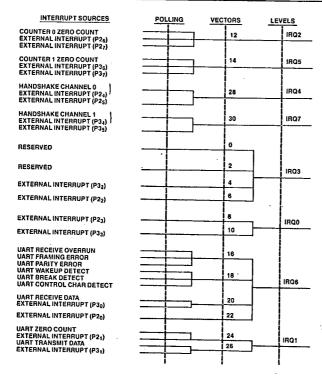

- Interrupt structure supports:

- ☐ 27 interrupt sources

- ☐ 16 Interrupt vectors (2 reserved for future versions)

- □ 8 interrupt levels

- ☐ Servicing in 600 nsec. (1 level only)

- Full-duplex UART with special features.

- On-chip oscillator.

- 20 MHz clock.

- 8K byte ROM for Z8820

# **GENERAL DESCRIPTION**

The Zilog Super8 single-chip MCU can be used for development and production. It can be used as I/O- or memory-intensive computers, or configured to address external memory while still supporting many I/O lines.

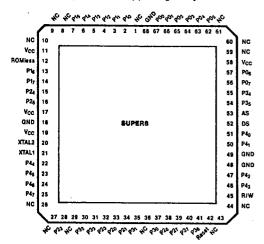

Figure 1a. Pin Assignments - 68-pin PLCC

The Super8 features a full-duplex universal asynchronous receiver/transmitter (UART) with on-chip baud rate generator, two programmable counter/timers, a direct memory access (DMA) controller, and an on-chip oscillator.

The Super8 is also available as a 48-pin and 68-pin ROMless microcomputer with four byte-wide I/O ports plus a byte-wide address/data bus. Additional address bits can be configured, up to a total of 16.

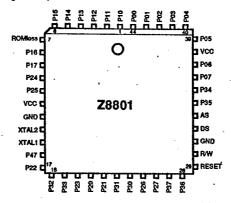

Figure 1b. Pin Assignments - 48-pin DIP

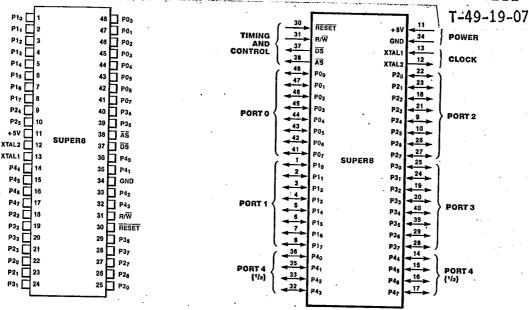

Figure 2. Pin Functions

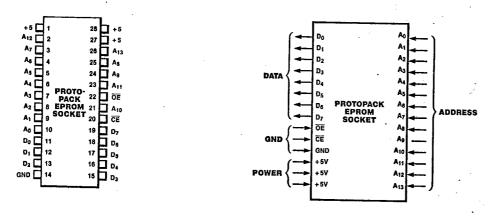

Figure 3. Pin Assignments—28-Pin Piggyback Socket

Figure 4. Pin Functions—28-Pin Piggyback Socket

# Protopack

This part functions as an emulator for the basic microcomputer. It uses the same package and pin-out as the basic microcomputer but also has a 28-pin "piggy back" socket on the top into which a ROM or EPROM can be installed. The socket is designed to accept a type 2764 EPROM.

This package permits the protopack to be used in prototype and final PC boards while still permitting user program

development. When a final program is developed, it can be mask-programmed into the production microcomputer device, directly replacing the emulator. The protopack part is also useful in situations where the cost of mask-programming is prohibitive or where program flexibility is desired.

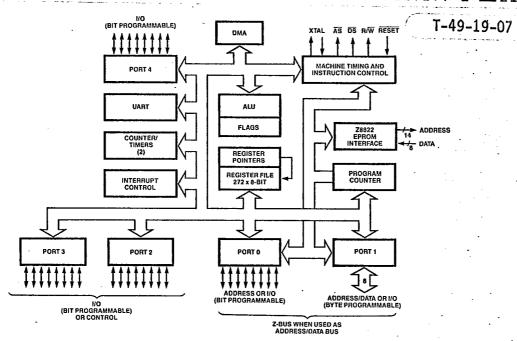

Figure 5. Functional Block Diagram

# **ARCHITECTURE**

The Super8 architecture includes 325 byte-wide internal registers. 272 of these are available for general purpose use; the remaining 53 provide control and mode functions.

The instruction set is specially designed to deal with this large register set. It includes a full complement of 8-bit arithmetic and logical operations, including multiply and divide instructions and provisions for BCD operations. Addresses and counters can be incremented and decremented as 16-bit quantities. Rotate, shift, and bit manipulation instructions are provided. Three new instructions support threaded-code languages.

The UART is a full-function multipurpose asynchronous serial channel with many premium features.

The 16-bit counters can operate independently of be cascaded to perform 32-bit counting and timing operations. The DMA controller handles transfers to and from the register file or memory. DMA can use the UART or one of two ports with handshake capability.

The architecture appears in the block diagram (Figure 5).

# **PIN DESCRIPTIONS**

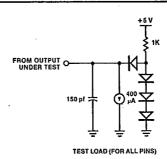

The Super8 connects to external devices via the following TTL-compatible pins:

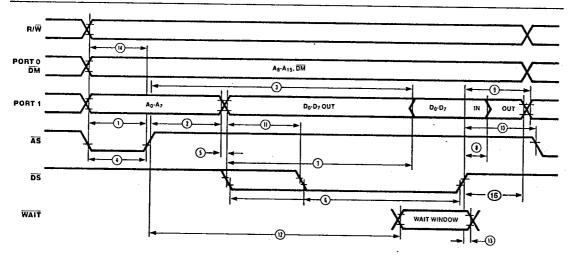

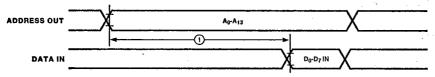

$\overline{\text{AS.}}$  Address Strobe (output, active Low).  $\overline{\text{AS}}$  is pulsed Low once at the beginning of each machine cycle. The rising edge indicates that addresses  $\overline{\text{RW}}$  and  $\overline{\text{DM}}$ , when used, are valid.

**DS.** Data Strobe (output, active Low).  $\overline{DS}$  provides timing for data movement between the address/data bus and external memory. During write cycles, data output is valid at the leading edge of  $\overline{DS}$ . During read cycles, data input must be valid prior to the trailing edge of  $\overline{DS}$ .

P0<sub>0</sub>-P0<sub>7</sub>, P1<sub>0</sub>-P1<sub>7</sub>, P2<sub>0</sub>-P2<sub>7</sub>, P3<sub>0</sub>-P3<sub>7</sub>, P4<sub>0</sub>-P4<sub>7</sub>. Port I/O Lines (input/output). These 40 lines are divided into five 8-bit I/O ports that can be configured under program control for I/O or external memory interface.

In the ROMless devices, Port 1 is dedicated as a multiplexed address/data port, and Port 0 pins can be assigned as additional address lines; Port 0 non-address pins may be assigned as I/O. In the ROM and protopack, Port 1 can be assigned as input or output, and Port 0 can be assigned as input or output on a bit by bit basis.

Ports 2 and 3 can be assigned on a bit-for-bit basis as general I/O or interrupt lines. They can also be used as special-purpose I/O lines to support the UART, counter/timers, or handshake channels.

Port 4 is used for general I/O.

During reset, all port pins are configured as inputs (high impedance) except for Port 1 and Port 0 in the ROMless devices. In these, Port 1 is configured as a multiplexed address/data bus, and Port 0 pins P0<sub>0</sub>-P0<sub>4</sub> are configured as address out, while pins P0<sub>5</sub>-P0<sub>7</sub> are configured as inputs.

**RESET.** Reset (input, active Low). Reset initializes and starts the Super8. When it is activated, it halts all processing; when

it is deactivated, the Super8 begins processing at address 0020<sub>H</sub>. T-49-19-07

**ROMIess.** (input, active High). This input controls the operation mode of a 68-pin Super8. When connected to  $V_{CC}$ , the part will function as a ROMIess Z8800. When connected to GND, the part will function as a Z8820 ROM part.

**R/W.** Read/Write (output). R/W determines the direction of data transfer for external memory transactions. It is Low when writing to program memory or data memory, and High for everything else.

XTAL1, XTAL2. (Crystal oscillator input.) These pins connect a parallel resonant crystal or an external clock source to the on-board clock oscillator and buffer.

# **REGISTERS**

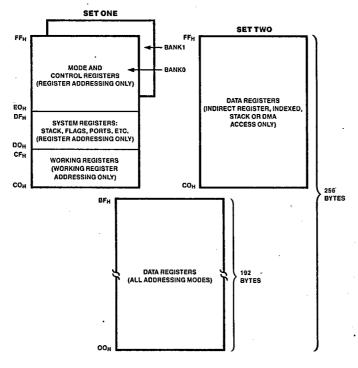

The Super8 contains a 256-byte internal register space. However, by using the upper 64 bytes of the register space more than once, a total of 325 registers are available.

Registers from 00 to BF are used only once. They can be accessed by any register command. Register addresses C0 to FF contain two separate sets of 64 registers. One set, called control registers, can only be accessed by register direct commands. The other set can only be addressed by register indirect, indexed, stack, and DMA commands.

The uppermost 32 register direct registers (E0 to FF) are further divided into two banks (0 and 1), selected by the Bank Select bit in the Flag register. When a Register Direct command accesses a register between E0 and FF, it looks at the Bank Select bit in the Flag register to select one of the banks.

The register space is shown in Figure 6.

Figure 6. Super8 Registers

# **Working Register Window**

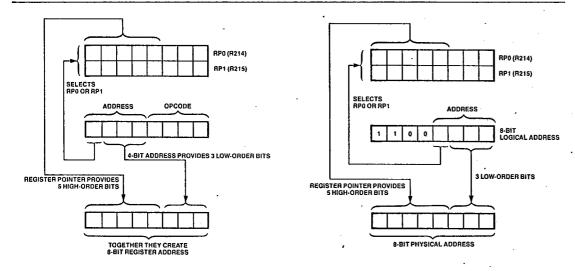

Control registers R214 and R215 are the register pointers, RP0 and RP1. They each define a moveable, 8-register section of the register space. The registers within these spaces are called working registers.

Working registers can be accessed using short 4-bit addresses. The process, shown in section a of Figure 4, works as follows:

- The high-order bit of the 4-bit address selects one of the two register pointers (0 selects RP0; 1 selects RP1).

- The five high-order bits in the register pointer select an 8-register (contiguous) slice of the register space.

- The three low-order bits of the 4-bit address select one of the eight registers in the slice.

a. 4-Bit Addressing

T-49-19-07

The net effect is to concatenate the five bits from the register pointer to the three bits from the address to form an 8-bit address. As long as the address in the register pointer remains unchanged, the three bits from the address will always point to an address within the same eight registers.

The register pointers can be moved by changing the five high bits in control registers R214 for RP0 and R215 for RP1.

The working registers can also be accessed by using full 8-bit addressing. When an 8-bit logical address in the range 192 to 207 (C0 to CF) is specified, the lower nibble is used similarly to the 4-bit addressing described above. This is shown in section b of Figure 7.

b. 8-Bit Addressing

Figure 7. Working Register Window

# 30E D 📟 9984043 0017080 6 💌 ZIL

Since any direct access to logical addresses 192 to 207 involves the register pointers, the physical registers 192 to 207 can be accessed only when selected by a register pointer. After a reset, RP0 points to R192 and RP1 points to R200.

Register List T-49-19-07

Table 1 lists the Super8 registers. For more details, see Figure 8.

Table 1. Super-8 Registers

| Addre              |             |                |                                     |

|--------------------|-------------|----------------|-------------------------------------|

| Decimal            | Hexadecimal | Mnemonic       | Function                            |

| eneral-Purpose Reg | isters      | ,              |                                     |

| 000-192            | 00-BF       |                | General purpose (all address modes) |

| 192-207            | C0-CF       | <del>-</del> . | Working register (direct only)      |

| 192-255            | C0-FF       |                | General purpose (indirect only)     |

| ode and Control Re | gisters     |                |                                     |

| 208                | D0          | P0             | Port 0 I/O bits                     |

| 209                | D1          | , P1           | Port 1 (I/O only)                   |

| 210                | D2          | P2             | Port 2                              |

| 211                | D3          | P3             | Port 3                              |

| 212                | D4          | P4             | Port 4                              |

| 213                | D5 .        | FLAGS          | System Flags Register               |

| 214                | D6          | RP0            | Register Pointer 0                  |

| 215                | D7          | RP1            | Register Pointer 1                  |

| 216                | D8          | SPH            | Stack Pointer High Byte             |

| 217                | D9          | SPL            | Stack Pointer Low Byte              |

| 218                | DA          | IPH            | Instruction Pointer High Byte       |

| 219                | DB          | IPL            | Instruction Pointer Low Byte        |

| 220                | DC          | IRQ            | Interrupt Request                   |

| 221                | DĎ          | IMR            | • • •                               |

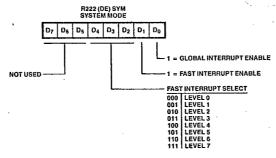

| 222                | DE          | SYM            | Interrupt Mask Register             |

| 222<br>224         |             |                | System Mode                         |

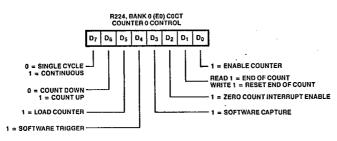

| 224                | E0 Bank 0   | COCT           | . CTR 0 Control                     |

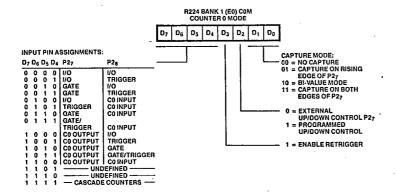

| 005                | Bank 1      | COM            | CTR 0 Mode                          |

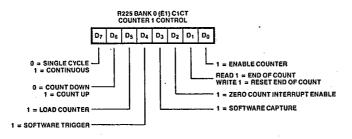

| 225                | E1 Bank 0   | C1CT           | CTR 1 Control                       |

|                    | Bank 1      | C1M .          | CTR 1 Mode                          |

| 226                | E2 Bank 0   | , COCH         | CTR 0 Capture Register, bits 8-15   |

|                    | Bank 1      | CTCH           | CTR 0 Timer Constant, bits 8-15     |

| 227                | E3 Bank 0   | COCL ,         | CTR 0 Capture Register, bits 0-7    |

| š.                 | Bank 1      | CTCL           | CTR 0 Time Constant, bits 0-7       |

| 228                | E4' Bank 0  | C1CH           | CTR 1 Capture Register, bits 8-15   |

|                    | Bank 1      | C1TCH          | CTR 1 Time Constant, bits 8-15      |

| 229                | E5 Bank 0   | C1CL           | CTR 1 Capture Register, bits 0-7    |

|                    | Bank 1      | C1TCL          | CTR 1 Time Constant, bits 0-7       |

| 235                | EB Bank 0   | ´UTC           | UART Transmit Control               |

| 236                | EC Bank 0   | URC            | UART Receive Control                |

| 237                | ED Bank 0   | UIE            | UART Interrupt Enable               |

| 239                | EF Bank 0   | UIO            | UART Data                           |

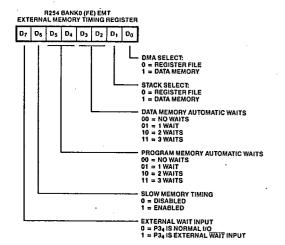

| 240                | F0 Bank 0   | POM            | Port 0 Mode                         |

|                    | Bank 1      | DCH            | DMA Count, bits 8-15                |

| 241                | F1 Bank 0   | PM             | Port Mode Register                  |

|                    | Bank 1      | DCL            | DMA Count, bits 0-7                 |

| 244                | . F4 Bank 0 | HOC            | Handshake Channel 0 Control         |

| 245                | F5 Bank 0   | H1C            | Handshake Channel 1 Control         |

| 246                | F6 Bank 0   | P4D            | Port 4 Direction                    |

| 247                | F7 Bank 0   | P4OD           |                                     |

| 248                |             |                | Port 4 Open Drain                   |

| 440                |             | . P2AM         | Port 2/3 A Mode                     |

|                    | Bank 1      | UBGH .         | UART Baud Rate Generator, bits 8-15 |

Table 1. Super-8 Registers (Continued)

| ٦ | -4 | ۵ | _1 | ٥ | _ | ۸ | 7 |

|---|----|---|----|---|---|---|---|

|   | -4 |   | -1 |   | _ | u | • |

| Addr                | ess                 |          |                                    |

|---------------------|---------------------|----------|------------------------------------|

| Decimal             | Hexadecimal         | Mnemonic | Function                           |

| lode and Control Re | gisters (Continued) |          |                                    |

| 249                 | F9 Bank 0           | P2BM     | Port 2/3 B Mode                    |

|                     | Bank 1              | UBGL     | UART Baud Rate Generator, bits 0-7 |

| 250                 | FA Bank 0           | P2CM     | Port 2/3 C Mode                    |

|                     | Bank 1              | UMA ·    | UART Mode A                        |

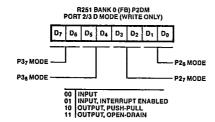

| 251                 | FB Bank 0           | P2DM     | Port 2/3 D Mode                    |

|                     | Bank 1              | UMB      | UART Mode B                        |

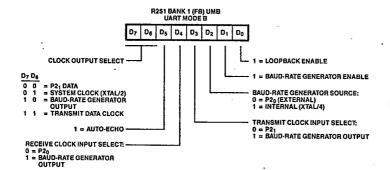

| 252                 | FC Bank 0           | P2AIP    | Port 2/3 A Interrupt Pending       |

| 253                 | FD Bank 0           | P2BIP    | Port 2/3 B Interrupt Pending       |

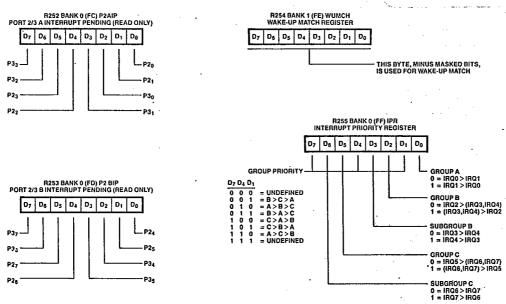

| 254                 | FE Bank 0           | EMT      | External Memory Timing             |

|                     | Bank 1              | WUMCH    | Wakeup Match Register              |

| 255                 | . FF Bank 0         | IPR      | Interrupt Priority Register        |

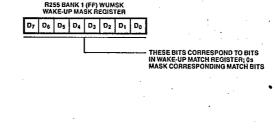

|                     | Bank 1              | WUMSK    | Wakeup Mask Register               |

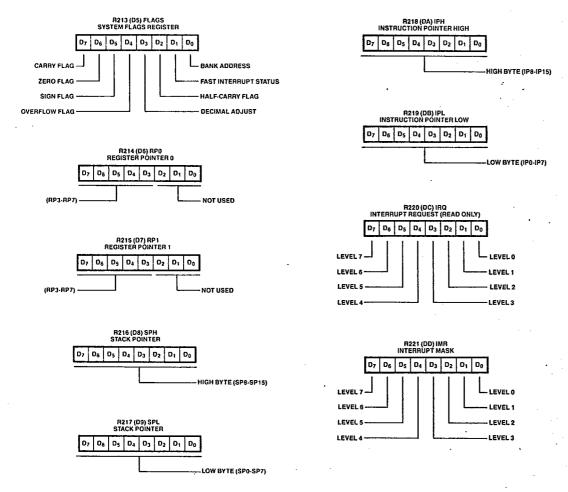

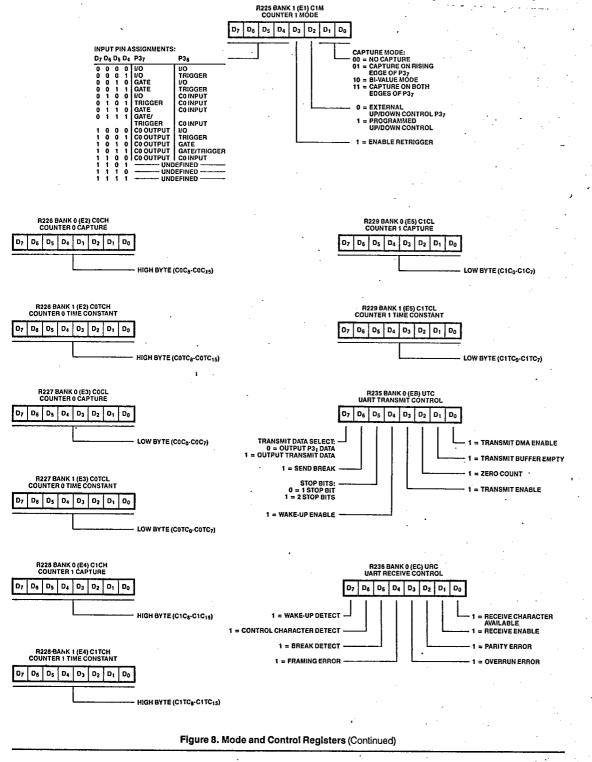

# **MODE AND CONTROL REGISTERS**

Figure 8. Mode and Control Registers

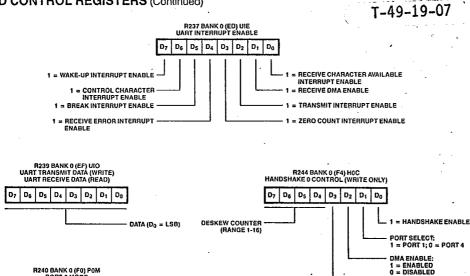

# MODE AND CONTROL REGISTERS (Continued)

T-49-19-07

Figure 8. Mode and Control Registers (Continued)

T-49-19-07

D6 D5 D4 D3 D2 D1 D0

P40-P47 I/O DIRECTION 0 = OUTPUT; 1 = INPUT

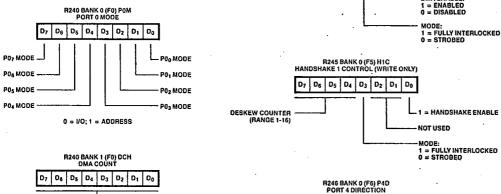

# MODE AND CONTROL REGISTERS (Continued)

HIGH BYTE (DC8-DC15)

Figure 8. Mode and Control Registers (Continued)

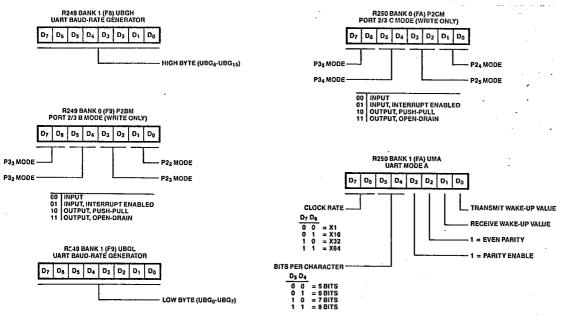

# MODE AND CONTROL REGISTERS (Continued)

T-49-19-07

Figure 8. Mode and Control Registers (Continued)

# MODE AND CONTROL REGISTERS (Continued)

T-49-19-07

Figure 8. Mode and Control Registers (Continued)

# T-49-19-07

# I/O PORTS

The Super8 has 40 I/O lines arranged into five 8-bit ports. These lines are all TTL-compatible, and can be configured as inputs or outputs. Some can also be configured as address/data lines.

Each port has an input register, an output register, and a register address. Data coming into the port is stored in the input register, and data to be written to a port is stored in the output register. Reading a port's register address returns the value in the input register; writing a port's register address loads the value in the output register. If the port is configured for an output, this value will appear on the external pins.

When the CPU reads the bits configured as outputs, the data on the external pins is returned. Under normal output loading, this has the same effect as reading the output register, unless the bits are configured as open-drain outputs.

The ports can be configured as shown in Table 2.

**Table 2. Port Configuration**

| Port    | Configuration Choices                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------|

| 0       | Address outputs and/or general I/O                                                                     |

| 1       | Multiplexed address/data(or I/O, only for ROM and Protopack)                                           |

| 2 and 3 | Control I/O for UART, handshake channels, and counter/timers; also general I/O and external interrupts |

| 4       | General I/O                                                                                            |

#### Port 0

Port 0 can be configured as an I/O port or an output for addressing external memory, or it can be divided and used as both. The bits configured as I/O can be either all outputs or all inputs; they cannot be mixed. If configured for outputs, they can be push-pull or open-drain type.

Any bits configured for I/O can be accessed via R208. To write to the port, specify R208 as the destination (dst) of an instruction; to read the port, specify R208 as the source (src).

Port 0 bits configured as I/O can be placed under handshake control of handshake channel 1.

Port 0 bits configured as address outputs cannot be accessed via the register.

In ROMless devices, initially the four lower bits are configured as address eight through twelve.

#### Port 1

In the ROMless device, Port 1 is configured as a byte-wide address/data port. It provides a byte-wide multiplexed address/data path. Additional address lines can be added by configuring Port 0.

The ROM and Protopack Port 1 can be configured as above or as an I/O port; it can be a byte-wide input, open-drain output, or push-pull output. It can be placed under handshake control or handshake channel 0.

#### Ports 2 and 3

Ports 2 and 3 provide external control inputs and outputs for the UART, handshake channels, and counter/timers. The pin assignments appear in Table 3.

Bits not used for control I/O can be configured as general-purpose I/O lines and/or external interrupt inputs.

Those bits configured for general I/O can be configured individually for input or output. Those configured for output can be individually configured for open-drain or push-pull output.

All Port 2 and 3 input pins are Schmitt-triggered.

The port address for Port 2 is R210, and for Port 3 is R211.

Table 3. Pin Assignments for Ports 2 and 3

| Port                    | 2                   | Port | 3                      |

|-------------------------|---------------------|------|------------------------|

| Bit<br>0<br>1<br>2<br>3 | Function            | Bit  | Function               |

| 0                       | UART receive clock  | 0    | UART receive data      |

| 1                       | UART transmit clock | 1    | UART transmit data     |

| 2                       | Reserved            | 2    | Reserved               |

| 3                       | Reserved            | 3    | Reserved               |

| 4                       | Handshake 0 input   | 4    | Handshake 1 input/WAIT |

| 5                       | Handshake 0 output  | 5    | Handshake 1 output/DM  |

| 6                       | Counter 0 input     | 6    | Counter 1 input        |

| 7                       | Counter 0 I/O       | 7.   | Counter 1 I/O          |

#### Port 4

Port 4 can be configured as I/O only. Each bit can be configured individually as input or output, with either push-pull or open-drain outputs. All Port 4 inputs are Schmitt-triggered.

Port 4 can be placed under handshake control of handshake channel 0. Its register address is R212.

# UART

The UART is a full-duplex asynchronous channel. It transmits and receives independently with 5 to 8 bits per character, has options for even or odd bit parity, and a wake-up feature.

Data can be read into or out of the UART via R239, Bank 0. This single address is able to serve a full-duplex channel because it contains two complete 8-bit registers—one for the transmitter and the other for the receiver.

#### Pins

The UART uses the following Port 2 and 3 pins:

| Port/Pin | <b>UART</b> Function |

|----------|----------------------|

| 2/0      | Receive Clock        |

| 3/0      | Receive Data         |

| 2/1      | Transmit Clock       |

| 3/1      | Transmit Data        |

# Transmitter

When the UART's register address is specified as the destination (dst) of an operation, the data is output on the UART, which automatically adds the start bit, the programmed parity bit, and the programmed number of stop bits. It can also add a wake-up bit if that option is selected.

If the UART is programmed for a 5-, 6-, or 7-bit character, the extra bits in R239 are ignored.

Serial data is transmitted at a rate equal to 1, 1/16, 1/32 or 1/64 of the transmitter clock rate, depending on the programmed data rate. All data is sent out on the falling edge of the clock input.

When the UART has no data to send, it holds the output marking (High). It may be programmed with the Send Break command to hold the output Low (Spacing), which it continues until the command is cleared.

# Receiver

30E D

# T-49-19-07

The UART begins receive operation when Receive Enable (URC, bit 0) is set High. After this, a Low on the receive input pin for longer than half a bit time is interpreted as a start bit. The UART samples the data on the input pin in the middle of each clock cycle until a complete byte is assembled. This is placed in the Receive Data register.

If the 1X clock mode is selected, external bit synchronization must be provided, and the input data is sampled on the rising edge of the clock.

For character lengths of less than eight bits, the UART inserts ones into the unused bits, and, if parity is enabled, the parity bit is not stripped. The data bits, extra ones, and the parity bit are placed in the UART Data register (UIO).

While the UART is assembling a byte in its input shift register, the CPU has time to service an interrupt and manipulate the data character in UIO.

Once a complete character is assembled, the UART checks it and performs the following:

- If it is an ASCII control character, the UART sets the Control Character status bit.

- It checks the wake-up settings and completes any indicated action.

- If parity is enabled, the UART checks to see if the calculated parity matches the programmed parity bit. If they do not match, it sets the Parity Error bit in URC (R236 Bank 0), which remains set until reset by software.

- It sets the Framing Error bit (URC, bit 4) if the character is assembled without any stop bits. This bit remains set until cleared by software.

Overrun errors occur when characters are received faster than they are read. That is, when the UART has assembled a complete character before the CPU has read the current character, the UART sets the Overrun Error bit (URC, bit 3), and the character currently in the receive buffer is lost.

The overrun bit remains set until cleared by software.

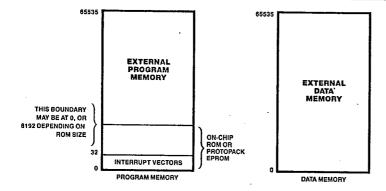

# **ADDRESS SPACE**

The Super8 can access 64K bytes of program memory and 64K bytes of data memory. These spaces can be either combined or separate. If separate, they are controlled by the  $\overline{\rm DM}$  line (Port P3<sub>5</sub>), which selects data memory when Low and program memory when High.

Figure 9 shows the system memory space.

# **CPU Program Memory**

Program memory occupies addresses 0 to 64K. External program memory, if present, is accessed by configuring Ports 0 and 1 as a memory interface.

The address/data lines are controlled by  $\overline{AS}$ ,  $\overline{DS}$  and  $R/\overline{W}$ .

The first 32 program memory bytes are reserved for interrupt vectors; the lowest address available for user programs is 32 (decimal). This value is automatically loaded into the program counter after a hardware reset.

# **ROMless**

Port 0 can be configured to provide from 0 to 8 additional address lines. Port 1 is always used as an 8-bit multiplexed address/data port.

T-49-19-07

# **ROM and Protopack**

Port 1 is configured as multiplexed address/data or as I/O. When Port 1 is configured as address/data, Port 0 lines can be used as additional address lines, up to address 15. External program memory is mapped above internal program memory; that is, external program memory can occupy any space beginning at the top of the internal ROM space up to the 64K (16-bit address) limit.

# **CPU Data Memory**

The external CPU data memory space, if separated from program memory by the  $\overline{DM}$  optional output, can be mapped anywhere from 0 to 64K (full 16-bit address space). Data memory uses the same address/data bus (Port 1) and additional addresses (chosen from Port 0) as program memory. Data memory is distinguished from program memory by the DM pin (P3<sub>5</sub>), and by the fact that data memory can begin at address 0000<sub>H</sub>. This feature differs from the Z8.

Figure 9. Program and Data Memory Address Spaces

# **INSTRUCTION SET**

The Super8 instruction set is designed to handle its large register set. The instruction set provides a full complement of 8-bit arithmetic and logical operations, including multiply and divide. It supports BCD operations using a decimal adjustment of binary values, and it supports incrementing and decrementing 16-bit quantities for addresses and counters.

It provides extensive bit manipulation, and rotate and shift operations, and it requires no special I/O instructions—the I/O ports are mapped into the register file.

#### Instruction Pointer

A special register called the Instruction Pointer (IP) provides hardware support for threaded-code languages. It consists of register-pair R218 and R219, and it contains memory addresses. The MSB is R218.

Threaded-code languages deal with an imaginary higher-level machine within the existing hardware machine. The IP acts like the PC for that machine. The command NEXT passes control to or from the hardware machine to the imaginary machine, and the commands ENTER and EXIT are imaginary machine equivalents of (real machine) CALLS and RETURNS.

If the commands NEXT, ENTER, and EXIT are not used, the IP can be used by the fast interrupt processing, as described in the Interrupts section.

# Flag Register

The Flag register (FLAGS) contains eight bits that describe the current status of the Super8. Four of these can be tested and used with conditional jump instructions; two others are used for BCD arithmetic. FLAGS also contains the Bank Address bit and the Fast Interrupt Status bit.

The flag bits can be set and reset by instructions.

#### CAUTION

Do not specify FLAGS as the destination of an instruction that normally affects the flag bits or the result will be unspecified.

# T-49-19-07

The following paragraphs describe each flag bit:

Bank Address. This bit is used to select one of the register banks (0 or 1) between (decimal) addresses 224 and 255. It is cleared by the SB0 instruction and set by the SB1 instruction.

Fast Interrupt Status. This bit is set during a fast interrupt cycle and reset during the IRET following interrupt servicing. When set, this bit inhibits all interrupts and causes the fast interrupt return to be executed when the IRET instruction is fetched.

Half-Carry. This bit is set to 1 whenever an addition generates a carry out of bit 3, or when a subtraction borrows out of bit 4. This bit is used by the Decimal Adjust (DA) instruction to convert the binary result of a previous addition or subtraction into the correct decimal (BCD) result. This flag, and the Decimal Adjust flag, are not usually accessed by users.

**Decimal Adjust.** This bit is used to specify what type of instruction was executed last during BCD operations, so a subsequent Decimal Adjust operation can function correctly. This bit is not usually accessible to programmers, and cannot be used as a test condition.

**Overflow Flag.** This flag is set to 1 when the result of a twos-complement operation was greater than 127 or less than -128. It is also cleared to 0 during logical operations.

**Sign Flag.** Following arithmetic, logical, rotate, or shift operations, this bit identifies the state of the MSB of the result. A 0 indicates a positive number and a 1 indicates a negative number.

**Zero Flag.** For arithmetic and logical operations, this flag is set to 1 if the result of the operation is zero.

For operations that test bits in a register, the zero bit is set to 1 if the result is zero.

For rotate and shift operations, this bit is set to 1 if the result is zero.

**Carry Flag.** This flag is set to 1 if the result from an arithmetic operation generates a carry out of, or a borrow into, bit 7.

After rotate and shift operations, it contains the last value shifted out of the specified register.

It can be set, cleared, or complemented by instructions.

# **Condition Codes**

The flags C, Z, S, and V are used to control the operation of conditional jump instructions.

The opcode of a conditional jump contains a 4-bit field called the condition code (cc). This specifies under which conditions it is to execute the jump. For example, a conditional jump with the condition code for "equal" after a compare operation only jumps if the two operands are equal.

The condition codes and their meanings are given in Table 4.

# Addressing Modes

T-49-19-07

All operands except for immediate data and condition codes are expressed as register addresses, program memory addresses, or data memory addresses. The addressing modes and their designations are:

Register (R)

Indirect Register (IR)

Indexed (X)

Direct (DA)

Relative (RA)

Immediate (IM)

Indirect (IA)

Table 4. Condition Codes and Meanings

| Binary | Mnemonic | Flags                 | Meaning .                                         |

|--------|----------|-----------------------|---------------------------------------------------|

| 0000   | F        | _                     | Always false                                      |

| 1000   | _        | -                     | Always true                                       |

| 0111*  | С        | C = 1                 | Carry                                             |

| 1111*  | NC       | C=0                   | No carry                                          |

| 0110*  | Z        | Z = 1                 | Zero                                              |

| 1110*  | NZ       | Z=0                   | Not zero                                          |

| 1101   | PL       | S=0                   | Plus                                              |

| 0101   | MI       | S = 1                 | Minus                                             |

| 0100   | OV       | V == 1                | Overflow                                          |

| 1100   | NOV      | V = 0                 | No overflow                                       |

| 0110*  | EQ       | Z=1                   | Equal                                             |

| 1110*  | NE       | Z=0                   | Not equal                                         |

| 1001   | GE       | (S XOR V) = 0         | Greater than or equal                             |

| 0001   | LT       | (S XOR V) = 1         | Less than                                         |

| 1010 • | GT       | (Z OR (S XOR V)) = 0  | Greater than                                      |

| 0010   | LE       | (Z OR (S XOR V)) = 1  | Less than or equal                                |

| 1111*  | UGE      | C=0                   | Unsigned greater than or equal                    |

| 0111*  | ULT      | C=1                   | Unsigned less than                                |

| 1011   | UGT      | (C = 0 AND Z = 0) ≈ 1 | Unsigned less than                                |

| 0011   | ULE      | (C OR Z) = 1          | Unsigned greater than Unsigned less than or equal |

NOTE: Asterisks (\*) indicate condition codes that relate to two different mnemonics but test the same flags. For example, Z and EQ are both True if the Zero flag is set, but after an ADD instruction, Z would probably be used, while after a CP instruction, EQ would probably be used.

Registers can be addressed by an 8-bit address in the range of 0 to 255. Working registers can also be addressed using 4-bit addresses, where five bits contained in a register pointer (R218 or R219) are concatenated with three bits from the 4-bit address to form an 8-bit address.

Registers can be used in pairs to generate 16-bit program or data memory addresses.

# Notation and Encoding

T-49-19-07

The instruction set notations are described in Table 5.

# **Functional Summary of Commands**

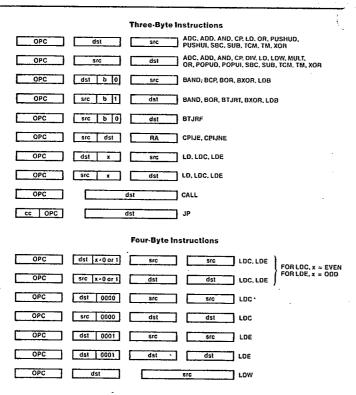

Figure 10 shows the formats followed by a quick reference guide to the commands.

# Table 5. Instruction Set Notations

| Notation | Meaning                                                  | Notation | Meaning                              |

|----------|----------------------------------------------------------|----------|--------------------------------------|

| CC       | Condition code (see Table 4)                             | DA       | Direct address (between 0 and 65535) |

| ſ        | Working register (between 0 and 15)                      | RA       | Relative address                     |

| rb       | Bit of working register                                  | IM       | Immediate                            |

| rO       | Bit 0 of working register                                | IML      | Immediate long                       |

| R        | Register or working register                             | dst      | Destination operand                  |

| RR       | Register pair or working register pair (Register pairs   | src      | Source operand                       |

| •        | always start on an even-number boundary)                 | @        | Indirect address prefix              |

| IA       | Indirect address                                         | SP       | Stack pointer                        |

| lr.      | Indirect working register                                | PC       | Program counter                      |

| iR       | Indirect register or indirect working register           | IP       | Instruction pointer                  |

| Irr      | Indirect working register pair                           | FLAGS    | Flags register                       |

| IRR      | Indirect register pair or indirect working register pair | RP       | Register pointer                     |

| X        | Indexed                                                  | #        | Immediate operand prefix             |

| XS       | Indexed, short offset                                    | %        | Hexadecimal number prefix            |

| XL       | Indexed, long offset                                     | OPG      | Opcode                               |

#### One-Byte Instructions

|             | F, DI. EI. ENTER. EXIT. IRET, NEXT. NOP.<br>F, RET. SBO, SB1. SCF, WFI                |

|-------------|---------------------------------------------------------------------------------------|

| dst OPC INC | · ·                                                                                   |

|             | Two-Byte Instructions                                                                 |

| OPC         | dst src ADC, ADD, AND, CP, LD, LDC, LDCI, LDCD, LDE, LDED, OR, SBC, SUB, TCM, TM, XOR |

| OPC         | src dst LDC, LOCPD, LDCPI, LDE, LDEPD, LDEPI                                          |

| OPC         | CALL, DA, DEC, DECW. INC, INCW, JP, POP, RL, RLC, RR, RRC, SWAP, CLR, SRA, COM        |

| OPC         | STC PUSH, SRP, SRP0, SRP1                                                             |

| OPC         | dst b 0 BITC, BITR                                                                    |

| OPC         | dsi b 1 BiTS                                                                          |

| r OPC       | dst DJNZ                                                                              |

| cc OPC      | dst JR                                                                                |

| dst OPC     | src LO                                                                                |

| src OPC     | dst LD                                                                                |

Figure 10. Instruction Formats

Figure 10. Instruction Formats (Continued)

# **INSTRUCTION SUMMARY**

| Instruction                        | Addr     | Mode          | Opcode        | Flags Affected |   |   |   |   |   |  |  |  |  |

|------------------------------------|----------|---------------|---------------|----------------|---|---|---|---|---|--|--|--|--|

| and Operation                      | dst      | src           | Byte<br>(Hex) | С              | Z | s | ٧ | D | Н |  |  |  |  |

| ADC dst,src<br>dst ← dst + src + C | (No      | te 1)         | 1□            | *              | * | * | _ | 0 | * |  |  |  |  |

| ADD dst,src<br>dst ← dst + src     | (No      | te 1)         | 0□            | *              | * | * | * | 0 | * |  |  |  |  |

| AND dst,src . dst ← dst AND src    | (No      | te 1)         | 5□            | _              | * | * | 0 |   | _ |  |  |  |  |

| BAND dst,src<br>dst ← dst AND src  | r0<br>Rb | Rb<br>r0      | 67<br>67      | _              | * | 0 | U | _ | _ |  |  |  |  |

| BCP dst, src<br>dst - src          | r0       | Rb            | 17            |                | * | 0 | U | - | _ |  |  |  |  |

| BITC dst<br>dst ← NOT dst          | rb       |               | 57            | -              | * | 0 | U | _ | _ |  |  |  |  |

| BITR dst<br>dst ← 0                | rb       |               | 77            | _              | _ | _ | _ | _ | _ |  |  |  |  |

| BITS dst<br>dst ← 1                | rb       | <del></del> - | 77            | _              | _ | _ | _ | _ | _ |  |  |  |  |

| Instruction              | Addr  | Mode | Opcode        | Flags Affected |          |   |   |   |   |  |  |  |

|--------------------------|-------|------|---------------|----------------|----------|---|---|---|---|--|--|--|

| and Operation            | dst   | src  | Byte<br>(Hex) | С              | z        | s | ٧ | D | Н |  |  |  |

| BOR dst, src             | r0    | rB   | 07            | _              | *        | 0 | U | _ | _ |  |  |  |

| dst ← dst OR src         | Rb    | r0   |               |                |          |   |   |   |   |  |  |  |

| BTJRF                    | RA    | rb   | 37            |                |          | _ | _ |   | _ |  |  |  |

| if $src = 0$ , $PC = PC$ | + dst |      |               |                |          | , |   |   |   |  |  |  |

| BTJRT                    | RA    | rb   | 37            | _              |          | ÷ | _ | _ |   |  |  |  |

| if src = 1, PC = PC      | + dst |      |               |                |          |   |   |   |   |  |  |  |

| BXOR dst, src            | rO    | Rb   | 27            | _              | *        | 0 | U | _ | _ |  |  |  |

| dst ← dst XOR src        | Rb    | r0   | 27            |                |          |   |   |   |   |  |  |  |

| CALL dst                 | DA    |      | F6            | _              | _        | _ | _ |   | _ |  |  |  |

| SP ← SP - 2              | IRR   |      | F4            |                |          |   |   |   |   |  |  |  |

| @SP ← PC                 | IA    |      | D4            |                |          |   |   |   |   |  |  |  |

| PC ← dst                 |       |      |               |                |          |   |   |   |   |  |  |  |

| CCF                      |       |      | EF            | *              | <u>-</u> | _ |   | _ | _ |  |  |  |

| C = NOT C                |       |      |               |                |          |   |   |   |   |  |  |  |

| CLR dst                  | R     |      | B0            | `              | _        | _ | _ | _ |   |  |  |  |

| dst ← 0                  | IR    |      | B1            |                |          |   |   |   |   |  |  |  |

# INSTRUCTION SUMMARY (Continued)

T-49-19-07

|                                                      | Addr    | Mode  | Opcode         | F   | lag | s A | Aff | ec       | tec | • |                                                                     | ddri     | Vlode   | •                  | Fla          | gs | Af  | fec | cted   |

|------------------------------------------------------|---------|-------|----------------|-----|-----|-----|-----|----------|-----|---|---------------------------------------------------------------------|----------|---------|--------------------|--------------|----|-----|-----|--------|

| Instruction and Operation                            | dst     | src   | Byte<br>(Hex)  | C   | z   | s   | ٧   | , I      | D I | H | Instruction and Operation                                           | dst      | src     | Byte<br>(Hex)      | C            | Z  | S   | ٧   | DН     |

| COM dst<br>dst ← NOT dst                             | R       |       | 60<br>61       | _   | *   | *   | 0   | ) -      |     | _ |                                                                     | RR<br>IR |         | A0<br>A1           | - 1          | *  | * : | k   |        |

| CP dst,src<br>dst - src                              | (No     | te 1) | Α□             | *   | *   | *   | *   |          |     |   | IRET (Fast)<br>PC ↔ IP                                              |          |         | BF                 | Rest<br>befo |    |     |     | ıpt    |

| CPIJE<br>if dst - src = 0,then                       | r       | İr    | C2             | _   | _   | _   |     |          |     | _ | FLAG ← FLAG'<br>FIS ← 0                                             |          |         |                    |              |    |     |     | ·<br>— |

| PC ← PC + RA<br>Ir ← Ir + 1                          |         |       |                |     |     |     |     |          |     |   | IRET (Normal)  FLAGS ← @SP; SP ← SP + |          |         | BF<br>0) ← 1       | Resi         |    |     |     | ıpt    |

| CPIJNE                                               | r       | lr    | D2             | -   | _   | -   | -   |          |     | - |                                                                     | DA       |         | ccD                | <u> </u>     |    |     |     |        |

| if dst - src = 0,then<br>PC ← PC + RA<br>Ir ← Ir + 1 |         |       |                |     |     |     |     |          |     |   | if cc is true,                                                      | IRR      |         | (cc = 0 to F)      | )            |    |     |     |        |

| DA dst                                               | R       |       | 40             | *   | *   | *   |     | ٠ ر      | _   | _ | JR cc,dst                                                           | RA       |         | ccB                |              |    | _   |     |        |

| dst ← DA dst                                         | IR<br>R |       | 41             |     |     | _   |     | _        |     |   | if cc is true,<br>PC ← PC + d                                       |          |         | (cc = 0 to F       | )            |    |     |     |        |

| DEC dst<br>dst ← dst – 1                             | IR      |       | 01             |     | -   | 75  |     | •        |     |   | LD dst,src                                                          | r        | IM      | rC                 | _            |    | _   |     |        |

| DECW dst                                             | RR      |       | 80             |     |     | _   |     | <u> </u> |     | _ | dst ← src                                                           | r        | R       | r8                 |              |    |     |     |        |

| dst ← dst – 1                                        | IR      |       | 81             |     | _   | _   |     | •        |     |   |                                                                     | R        | r       | r9<br>(r = 0 to F) | •            |    |     |     |        |

| DI                                                   |         |       | 8F             | -   | -   | -   |     | -        | _   | - |                                                                     | r<br>IR  | IR<br>r | C7<br>D7           |              |    |     |     |        |

| SMR (0) ← 0                                          |         |       |                |     |     |     | _   |          |     |   |                                                                     | R        | Ŕ       | . E4               |              |    |     |     |        |

| DIV dst, src                                         |         | _     |                |     |     |     |     |          |     |   | •                                                                   | R        | IR      | E5                 |              |    |     |     |        |

| dst ÷ src                                            | RR      | R     | 94             | . * | *   | *   | *   | *        | _   | _ |                                                                     | R        | IM      | E6                 |              |    |     |     |        |

| dst (Upper) ←<br>Quotient                            | RR      | IR    | 95             |     |     |     |     |          |     |   |                                                                     | IR       | IM      | D6                 |              |    |     |     |        |

| dst (Lower) ←                                        | RR      | IM    | 96             |     |     |     |     |          |     |   |                                                                     | IR<br>r  | R<br>x  | F5<br>87           |              |    |     |     |        |

| Remainder                                            |         |       |                |     |     |     |     |          |     | _ |                                                                     | X        | r       | 97                 |              |    |     |     |        |

| DJNZ r,dst                                           | RA      | r     | rA             | -   |     | -   |     | _        | _   | - | LDB dst, src                                                        | r0       | Rb      | 47                 |              |    | _   |     |        |

| r←r – 1                                              |         |       | (r = 0  to  F) |     |     |     |     |          |     |   | dst ← src                                                           | Rb       | rO      | 47                 |              |    |     |     |        |

| if r = 0<br>PC ← PC + dst                            |         |       |                |     |     |     |     |          |     |   | LDC/LDE                                                             | r        | irr     | СЗ                 |              | ÷  |     |     |        |

|                                                      |         |       | 9F             |     |     |     | _   | _        | _   | _ | dst ← src                                                           | irr      | r       | D3                 |              |    |     |     |        |

| <b>EI</b><br>SMR (0) ← 1                             |         |       | 91             | _   | _   |     |     |          | _   |   |                                                                     | r        | XS      | E7                 |              |    |     |     |        |

|                                                      |         |       |                |     |     |     |     |          |     |   |                                                                     | XS       | г<br>х1 | F7<br>A7           |              |    |     |     |        |

| ENTER                                                |         |       | 1F             | _   |     |     |     | _        |     |   |                                                                     | r<br>∙x1 | r       | B7                 |              |    |     |     |        |

| SP ← SP - 2<br>@ SP ← IP                             | •       |       |                |     |     |     |     |          |     |   |                                                                     | r        | DA.     |                    |              | •  |     |     |        |

| IP ← PC -                                            |         |       |                |     |     |     |     |          |     |   |                                                                     | DΑ       | r       | B7                 |              |    |     |     |        |

| PC ← @ IP<br>IP ← IP + 2                             |         |       |                |     |     |     |     |          |     |   | LDCD/LDED dst, src<br>dst ← src                                     | r        | Irr     | E2                 | _            | _  |     | -   |        |

| EXIT                                                 |         |       | 2F             | -   |     | -   | _   | _        | _   | _ | rr ← rr − 1                                                         |          |         |                    |              |    |     |     |        |

| IP ← @SP<br>SP ← SP + 2                              |         |       |                |     |     |     |     |          |     |   | LDEI/LDCI dst, src<br>dst ← src                                     | r        | İrr     | E3                 | _            | _  |     | -   |        |

| PC ← @IP<br>IP ← IP + 2                              |         |       |                |     |     |     |     |          |     |   | rr ← rr + 1                                                         |          |         |                    |              |    |     |     | -      |

| INC dst                                              | r       |       | rE             |     |     | _   | *   | +        | _   | _ | LDCPD/LDEPD dst,s                                                   |          |         |                    |              |    |     |     |        |

| dst ← dst + 1                                        | '       |       | (r = 0 to F    | )   | •   | • ' | -   | •        |     |   | rr ← rr – 1 '                                                       | irr      | r       | F2                 | _            | _  |     | _   |        |

|                                                      | R       |       | 20             | •   |     |     |     |          |     |   | dst ← src                                                           |          |         |                    | <u>.</u>     |    | -   |     |        |

|                                                      | IR      |       | 21             |     |     |     |     |          |     |   |                                                                     |          |         |                    |              |    |     |     |        |

# INSTRUCTION SUMMARY (Continued)

T-49-19-07

| Instruction                                                             | Addr     | Mode       | Opcode<br>Byte | Flags Affected |   |   |   |   |   |

|-------------------------------------------------------------------------|----------|------------|----------------|----------------|---|---|---|---|---|

| and Operation                                                           | dst      | src        | (Hex)          | С              | z | s | ٧ | D | Н |

| LDCPI/LDEPI dst, sre                                                    |          |            | <del></del>    |                | _ |   | _ |   |   |

| rr ← rr + 1<br>dst ← src                                                | irr      | r          | F3             | _              | _ | _ |   | _ | - |

| LDW dst, src                                                            | RR       | RR         | C4             | _              | _ | _ | _ | _ | _ |

| dst ← src                                                               | RR       | IR         | C5             |                |   |   |   |   |   |

|                                                                         | RR       | IMM        | C6             |                |   |   |   |   | _ |

| MULT dst, src                                                           | RR<br>RR | R<br>IR    | 84<br>85       | *              | 0 | * | * | _ | - |

|                                                                         | RR       | IM         | 86             |                |   |   |   |   |   |

| NEXT                                                                    |          |            | OF.            |                | _ | _ | _ | _ | _ |

| PC ← @IP                                                                |          |            | ٠.             |                |   |   |   | • |   |

| IP ← IP + 2                                                             |          |            |                |                |   |   |   |   |   |

| NOP                                                                     |          |            | FF             |                | _ | _ | _ | _ | _ |

| OR dst,src<br>dst ← dst OR src                                          | (No      | te 1)      | 4□             | _              | * | * | 0 | - | _ |

| POP dst                                                                 |          | R          | 50             | _              | _ | _ | _ | _ | _ |

| dst ← @SP;<br>SP ← SP + 1                                               |          | IR         | 51             | •              |   |   |   |   |   |

| POPUD dst, src<br>dst ← src                                             | R        | IR         | 92             | _              | _ |   | _ | _ | _ |

| IR ← IR ~ 1                                                             |          |            |                |                |   |   |   |   |   |

| POPUI dst, src                                                          | R        | IR         | 93             |                |   | _ |   | _ | _ |

| dst ← src                                                               |          |            |                |                |   |   |   |   |   |

| IR ← IR + 1                                                             |          |            |                |                |   |   |   |   |   |

| PUSH src                                                                |          | R          | 70             | _              | _ | _ |   | _ | - |

| SP ← SP - 1; @SP ←                                                      | src      | IR         | 71             |                |   |   |   |   |   |

| PUSHUD dst, src<br>IR ← IR – 1<br>dst ← src                             | IR       | R          | 82             |                | _ | _ | _ | _ |   |

| PUSHUI dst, src<br>IR ← IR + 1<br>dst ← src                             | IR       | R          | 83             | _              | _ | _ | _ | _ | _ |

| RCF<br>C ← 0                                                            |          | - <u> </u> | CF             | 0              |   | _ | _ | _ | _ |

| RET<br>PC ← @SP; SP ← SP                                                | + 2      |            | AF             | _              |   | _ |   | _ | _ |

| RL dst                                                                  | R        |            | 90             | *              | * | * | * | _ | _ |

| C ← dst (7)<br>dst (0) ← dst (7)<br>dst (N + 1) ← dst (N)<br>N = 0 to 6 | IR       |            | 91             | ٠              |   |   |   |   |   |

|                                                                                                                 |         |       |                |   | ٠   |     |              |      |    |

|-----------------------------------------------------------------------------------------------------------------|---------|-------|----------------|---|-----|-----|--------------|------|----|

| Instruction                                                                                                     | Addr    | Mode  | Opcode<br>Byte | F | lag | s A | Affe         | ecte | ₽d |

| and Operation                                                                                                   | dst     | src   | (Hex)          | C | Z   | S   | ٧            | Ď    | н  |

| RLC dst<br>dst (0) $\leftarrow$ C<br>C $\leftarrow$ dst (7)<br>dst (N + 1) $\leftarrow$ dst (N)<br>N = 0 to 6   | R<br>IR |       | 10<br>11       | * | *   | *   | *            |      |    |

| RR dst<br>$C \leftarrow dst(0)$<br>$dst(7) \leftarrow dst(0)$<br>$dst(N) \leftarrow dst(N + 1)$<br>N = 0  to  6 | R       |       | E0<br>E1       | * | *   | *   | *            |      | _  |

| RRC dst<br>C ← dst (0)<br>dst (7) ← C<br>dst (N) ← dst (N + 1)<br>N = 0 to 6                                    | R<br>IR |       | C0<br>C1       | * | *   | *   | *            | -    | .— |

| SB0<br>BANK ← 0                                                                                                 |         |       | 4F             |   | _   | _   | _            | _    | _  |

| SB1<br>BANK ← 1                                                                                                 |         |       | 5F             | _ | -   | _   | _            | _    | _  |

| SBC dst,src<br>dst ← dst – src – C                                                                              | (No     | te 1) | 3□             | * | *   | *   | *            | 1    | *  |

| <b>SCF</b><br>C ← 1                                                                                             |         |       | DF             | 1 | _   | -   | _            |      | _  |

| SRA dst dst (7) ← dst (7) C ← dst (0) dst (N) ← dst (N + 1) N = 0 to 6                                          | R<br>IR |       | D0<br>D1       | * | *   | *   | 0            | _    |    |

| SRP src<br>RP0 ← IM<br>RP1 ← IM + 8                                                                             |         | IM    | 31             | _ | _   | _   |              | _    | _  |

| SRP0<br>RP0 ← IM                                                                                                |         | IM    | 31             | _ | _   | _   |              | _    |    |

| SRP1<br>RP1 ←IM                                                                                                 |         | IM    | - 31           | _ | _   |     | <del>-</del> | _    | _  |

| SUB dst,src<br>dst ← dst – src                                                                                  | (Not    | e 1)  | 2□             | * | *   | *   | *            | 1    | *  |

|                                                                                                                 |         |       |                |   | _   |     | _            |      |    |

# **INSTRUCTION SUMMARY** (Continued)

T-49-19-07

Table 6. Second Nibble

|                                    | Addr    | Mode   | Opcode        | F | lag | s A | ffe | cte | d |

|------------------------------------|---------|--------|---------------|---|-----|-----|-----|-----|---|

| Instruction<br>and Operation       | dst src |        | Byte<br>(Hex) | C | z   | s   | ٧   | D   | Н |

| SWAP dst<br>dst (0·3) ++ dst (4·7) | R<br>IR |        | F0<br>F1      | _ | *   | *   | U   | _   | _ |

| TCM dst,src<br>(NOT dst) AND src   | (No     | te 1)  | 6□            | _ | *   | *   | 0   | _   | _ |

| TM dst,src<br>dst AND src          | (No     | te 1)  | 7□            | _ | *   | *   | 0   | _   | _ |

| WFI                                |         |        | 3F            | _ | _   | _   | _   | _   |   |

| XOR dst,src<br>dst ← dst XOR src   | (No     | ote 1) | B□            |   | *   | *   | 0   |     | _ |

NOTE 1: These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble identifies the command, and is found in the table above. The second nibble, represented by a □, defines the addressing mode as shown in Table 6.:

| Addr | Mode | Lower         |

|------|------|---------------|

| dst  | src  | Opcode Nibble |

| r    | r    | 2             |

| r    | lr   | 3             |

| R    | R    | 4             |

| R    | ` IR | 5             |

| R    | IM   | 6             |

For example, to use an opcode represented as x□ with an "RR" addressing mode, use the opcode "x4."

- 0 = Cleared to Zero

- 1 = Set to One

- = Unaffected

- U = Undefined

# **SUPER-8 OPCODE MAP**

T-49-19-07

|                    |   |                                 |                                  |                                                        |                                                  |                                                   |                                                     | Low                                   | er Nibb                                             | le (He                                    | x)    |                             |                                     |                      |                  |                    |   |                |              |

|--------------------|---|---------------------------------|----------------------------------|--------------------------------------------------------|--------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|---------------------------------------|-----------------------------------------------------|-------------------------------------------|-------|-----------------------------|-------------------------------------|----------------------|------------------|--------------------|---|----------------|--------------|

|                    |   | 0                               | 1                                | 2                                                      | 3                                                | 4                                                 | 5                                                   | 6                                     | 7                                                   | 8                                         |       | 9                           | A                                   | В                    | C                | D                  |   | E              | F            |

|                    | 0 | DEC                             | 6<br>DEC<br>IR <sub>1</sub>      | 6<br>ADD<br>(1./2                                      | ADD<br>r <sub>1</sub> ,lr <sub>2</sub>           | 10<br>ADD<br>R <sub>2</sub> ,R <sub>1</sub>       | 10<br>ADD<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10<br>ADD<br>R <sub>1</sub> ,IM       | 10<br>BOR*                                          | 6<br>LD<br>r <sub>1</sub> ,R <sub>2</sub> | -   - | 6<br>LD<br>2.R <sub>1</sub> | 12/10<br>DJNZ<br>r <sub>1</sub> ,RA | 12/10<br>JR<br>cc,RA | 6<br>LD<br>(1,1M | 12/1<br>JP<br>cc,D |   | 6<br>INC<br>r1 | 14<br>NEXT   |

|                    | 1 | 6<br>RLC<br>R <sub>1</sub>      | 6<br>RLC<br>IR <sub>1</sub>      | 6<br>ADC<br>r <sub>1</sub> ,r <sub>2</sub>             | 6<br>ADC<br>r <sub>1</sub> ,lr <sub>2</sub>      | 10<br>ADC<br>R <sub>2</sub> ,R <sub>1</sub>       | 10<br>ADC<br>IR <sub>2</sub> R <sub>1</sub>         | 10<br>ADC<br>R <sub>1</sub> .IM       | 10<br>BCP<br>r <sub>1</sub> ,b.R <sub>2</sub>       |                                           |       |                             |                                     |                      |                  |                    |   | Ï              | 20<br>ENTER  |

|                    | 2 | 6<br>INC<br>R <sub>1</sub>      | 6<br>INC<br>IR <sub>1</sub>      | 6<br>SUB<br>r <sub>1</sub> ,r <sub>2</sub>             | 6<br>SUB<br>(1.l(2                               | 10<br>SUB<br>R <sub>2</sub> ,R <sub>1</sub>       | 10<br>SUB<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10<br>SUB<br>R <sub>1</sub> .IM       | 10<br>BXOR*                                         |                                           |       |                             |                                     |                      |                  |                    |   |                | 22<br>EXIT   |

|                    | 3 | 10<br>JP<br>IRR <sub>1</sub>    | NOTE<br>C                        | 6<br>SBC<br>r <sub>1</sub> .r <sub>2</sub>             | 6<br>SBC<br>r <sub>1</sub> ,lr <sub>2</sub>      | 10<br>SBC<br>R <sub>2</sub> ,R <sub>1</sub>       | 10<br>SBC<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10<br>SBC<br>R <sub>1</sub> .IM       | NOTE<br>A                                           |                                           |       |                             |                                     |                      |                  |                    |   |                | 6<br>WFI     |

|                    | 4 | 6<br>DA<br>R <sub>1</sub>       | 6<br>DA<br>IR <sub>1</sub>       | 6<br>OR<br>(1./2                                       | 6<br>OR<br>r <sub>1</sub> ,lr <sub>2</sub>       | 10<br>OR<br>R <sub>2</sub> ,R <sub>1</sub>        | 10<br>OR<br>IR <sub>2</sub> ,R <sub>1</sub>         | 10<br>OR<br>R <sub>1</sub> .iM        | 10<br>LDB*                                          |                                           |       |                             |                                     |                      |                  |                    |   |                | 6<br>SBO     |

|                    | 5 | POP<br>R <sub>1</sub>           | 10<br>POP<br>IR <sub>1</sub>     | 6<br>AND<br>11.12                                      | 6<br>AND<br>r <sub>1</sub> .lr <sub>2</sub>      | 10<br>AND<br>R <sub>2</sub> .R <sub>1</sub>       | 10<br>AND<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10<br>AND<br>R <sub>1</sub> .IM       | 8<br>BITC<br>r <sub>1</sub> ,b                      |                                           |       |                             |                                     |                      |                  |                    |   |                | 6<br>SBI     |

| Hex)               | 6 | COM<br>R <sub>1</sub>           | COM                              | 6<br>TCM<br>11.12                                      | 6<br>TCM<br>(1.lr <sub>2</sub>                   | 10<br>TCM<br>R <sub>2</sub> ,R <sub>1</sub>       | 10<br>TCM<br>IR <sub>2</sub> ,R <sub>1</sub>        | 10<br>TCM<br>R <sub>1</sub> .IM       | 10<br>BAND*<br>r <sub>0</sub> ·R <sub>b</sub>       |                                           |       |                             |                                     |                      |                  |                    |   |                |              |

| libble (I          | 7 | 10:12<br>PUSH<br>R <sub>2</sub> | 12/14<br>PUSH<br>IR <sub>2</sub> | 6<br>TM<br>(1./2                                       | 6<br>TM<br>rt,ir2                                | 10<br>TM<br>R <sub>2</sub> .R <sub>1</sub>        | 10<br>TM<br>IR <sub>2</sub> ,R <sub>1</sub>         | 10<br>TM<br>R <sub>1</sub> .IM        | NOTE<br>B                                           |                                           |       |                             |                                     |                      |                  |                    |   |                |              |

| Upper Nibble (Hex) | 8 | 10<br>DECW<br>RR <sub>1</sub>   | 10<br>DECW<br>IR <sub>1</sub>    | 10<br>PUSHUD<br>IR <sub>1</sub> .R <sub>2</sub>        | 10<br>PUSHUI<br>IR <sub>1</sub> .R <sub>2</sub>  | 24<br>MULT<br>R <sub>2</sub> ,RR <sub>1</sub>     | 24<br>MULT<br>IR <sub>2</sub> ,RR <sub>1</sub>      | 24<br>MULT<br>IM.RR;                  | 10<br><b>LD</b><br>r <sub>1</sub> .x.r <sub>2</sub> |                                           |       | į                           |                                     |                      |                  |                    |   |                | 6<br>DI      |

| _                  | 9 | 6<br>RL<br>R <sub>1</sub>       | 6<br>RL<br>IR <sub>1</sub>       | 10<br>POPUD<br>IR <sub>2.</sub> R <sub>1</sub>         | 10<br>POPUI<br>IR <sub>2</sub> ,R <sub>1</sub>   | 28/12<br>DIV<br>R <sub>2</sub> ,RR <sub>1</sub>   | 28/12<br>DIV<br>IR <sub>2</sub> ,RR <sub>1</sub>    | 28/12<br>DIV<br>IM,RR <sub>1</sub>    | 10<br>LD<br>r <sub>2</sub> .x,r <sub>1</sub>        |                                           | 1     |                             |                                     |                      |                  |                    |   |                | 6<br>El      |

|                    | A | 10<br>INCW<br>RR <sub>1</sub>   | 10<br>INCW<br>IR <sub>1</sub>    | 6<br>CP<br>r <sub>1.</sub> r <sub>2</sub>              | 6<br>CP<br>r <sub>1</sub> .lr <sub>2</sub>       | 10<br><b>CP</b><br>R <sub>2</sub> .R <sub>1</sub> | 10<br><b>CP</b><br>IR <sub>2</sub> ,R <sub>1</sub>  | 10<br>CP<br>R <sub>1</sub> ,IM        | NOTE<br>D                                           |                                           |       |                             |                                     |                      |                  |                    |   |                | 14<br>RET    |

|                    | В | 6<br>CLR<br>R <sub>1</sub>      | 6<br>CLR<br>IR,                  | 6<br>XOR<br>(1./2                                      | 6<br>XOR<br>r <sub>1</sub> .ir <sub>2</sub>      | 10<br>XOR<br>R <sub>2</sub> .R <sub>1</sub>       | 10<br><b>XOR</b><br>IR <sub>2</sub> ,R <sub>1</sub> | 10<br>XOR<br>R <sub>1</sub> ,IM       | NOTE<br>E                                           |                                           |       |                             |                                     |                      |                  |                    |   |                | 16/6<br>IRET |

|                    | С | 6<br>RAC<br>R <sub>1</sub>      | 6<br>RRC<br>IR <sub>1</sub>      | 16/18<br>CPIJE<br>Icr <sub>2</sub> ,RA                 | 11'ju5<br>FDC.                                   | 10<br>LDW<br>RR <sub>2</sub> ,RR <sub>1</sub>     | 10<br>LDW<br>IR <sub>2</sub> .RR <sub>1</sub>       | 12<br>LOW<br>RR <sub>1</sub> .IML     | 6<br><b>LD</b><br>r <sub>1.</sub> lr <sub>2</sub>   |                                           |       |                             |                                     |                      |                  |                    |   |                | 6<br>RCF     |

|                    | D | 6<br>SRA<br>R <sub>1</sub>      | 6<br>SRA<br>IR <sub>1</sub>      | 16/18<br>CPIJNE<br>Ir <sub>1</sub> .r <sub>2</sub> .RA | 12.lt.1                                          | 20<br>CALL<br>IA <sub>1</sub>                     |                                                     | 10<br>LD<br>IR <sub>1</sub> ,IM       | / 6<br>LD<br>lr <sub>1</sub> ,r <sub>2</sub>        |                                           |       |                             |                                     |                      |                  | ŀ                  |   |                | 6<br>SCF     |

|                    | E | 6<br>RA<br>R <sub>1</sub>       | 6<br>RR<br>IR <sub>1</sub>       | 11'ju5<br>rdcd.                                        | 16<br>LDCI*<br>r <sub>1.</sub> lrr <sub>2</sub>  | 10<br><b>LD</b><br>R <sub>2</sub> ,R <sub>1</sub> | 10<br>LD<br>IR <sub>2</sub> ,R <sub>1</sub>         | 10<br><b>LD</b><br>R <sub>1</sub> ,IM | 18<br>LDC*<br>r <sub>1</sub> ,lrr <sub>2</sub> ,xs  |                                           |       |                             |                                     |                      |                  |                    |   |                | 6<br>CCF     |

|                    | F | 8<br>SWAP<br>R <sub>1</sub>     | 8<br>SWAP<br>IR <sub>1</sub>     | 16<br>LDCPD*                                           | 16<br>LDCPI*<br>r <sub>2</sub> .lrr <sub>1</sub> | 18<br>CALL<br>IRR <sub>1</sub>                    | 10<br><b>LD</b><br>R <sub>2</sub> ,IR <sub>1</sub>  | 18<br>CALL<br>DA <sub>1</sub>         | 18<br>LDC*<br>r <sub>2</sub> .lrr <sub>1</sub> .xs  | <u> </u>                                  |       |                             |                                     |                      |                  |                    | , |                | 6<br>NOP     |

16/18 16/18 BTJRF BTJRT r<sub>2</sub>.b RA r<sub>2</sub>.b.RA NOTE A

8 BITR 8 BITS r<sub>1</sub>.b NOTE B

NOTE C

6 SRP IM 6 SRP0 IM 6 SRP1 IM

NOTE D

20 LDC\* r<sub>1</sub>.lrr<sub>2</sub>.xL 20 LDC\* r<sub>1</sub>.DA<sub>2</sub>

NOTEE

20 LDC\* r<sub>2</sub>.DA<sub>1</sub> 20 LDC\* r2,lrr2,xL

Legend:

r = 4-bit address

R = 8-bit address

b = bit number

R<sub>1</sub> or r<sub>1</sub> = dst address

R<sub>2</sub> or r<sub>2</sub> = src address

\*Examples:

BOR r<sub>0</sub>-R<sub>2</sub>

is BOR r<sub>1</sub>, b.R<sub>2</sub>

or BOR r<sub>2</sub>-b,R<sub>1</sub>

LDC r<sub>1</sub>.Irr<sub>2</sub> = program

or LDE r<sub>1</sub>.Irr<sub>2</sub> = data

Sequence: Opcode, first, second, third operands

NOTE: The blank areas are not defined.

Figure 11. Opcode Map

INSTRUCTIONS

T-49-19-07

Table 7. Super8 Instructions

| Vinemonic    | Operands     | Instruction                               | Mnemonic    | Operands         | Instruction                     |

|--------------|--------------|-------------------------------------------|-------------|------------------|---------------------------------|

| Load Instruc | ctions       |                                           | Program Co  | ntrol Instructio |                                 |

| CLR          | dst          | Clear                                     | BTJRT       | dst, src         | Bit test jump relative on True  |

| LD           | dst, src     | Load                                      | BTJRF       | dst, src         | Bit test jump relative on False |

| _DB          | dst, src     | Load bit                                  | CALL        | dst              | Call procedure                  |

| _DC          | dst, src     | Load program memory                       | CPIJE       | dst, src         | Compare, increment and jump on  |

| LDE          | dst, src     | Load data memory                          | _           |                  | equal                           |

| LDCD         | dst, src     | Load program memory and                   | CPIJNE      | dst, src         | Compare, increment and jump on  |

| _000         | 031, 310     | decrement                                 |             |                  | non-equal                       |

| LDED         | dst, src     | Load data memory and                      | DJNŽ        | r, dst           | Decrement and jump on non-zero  |

| LDLO         | dat, are     | decrement                                 | ENTER       |                  | Enter                           |

| _DCI         | dst, src     | Load program memory and                   | EXIT        |                  | Exit                            |

| _DC1         | dat, are     | increment                                 | IRET        | ·                | Return from interrupt           |

| חבו          | dat ara      | Load data memory and increment            | JP          | cc, dst          | Jump on condition code          |

| LDEI         | dst, src     | Load program memory with                  | JP          | dst              | Jump unconditional              |

| LDCPD        | dst, src     | pre-decrement                             | JR          | cc, dst          | Jump relative on condition code |